北京慧享天下科技有限公司

BEIJING HUIXIANG TIANXIA TECHNOLOGY CO., LTD.

新聞中心

News center

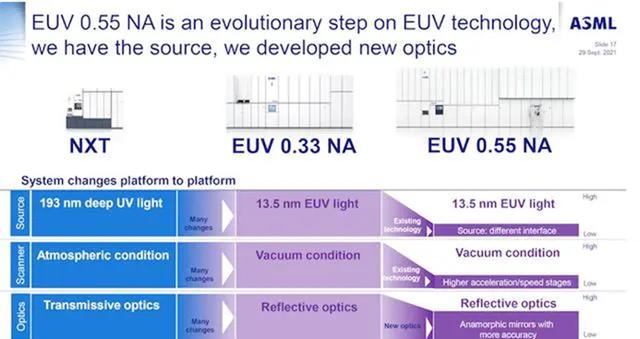

2024年,這些半導體技術值得期待

來源:

|

作者:網絡

|

發布(bu)時(shi)間: 629天前

|

522 次瀏覽(lan)

|

分(fen)享(xiang)到(dao):

北京慧享天下科技有限公司

BEIJING HUIXIANG TIANXIA TECHNOLOGY CO., LTD.

新聞中心

News center